# **ECE Department**

## **3<sup>rd</sup> BOS File**

# **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY**

## **AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

**Bhimavaram,**

**Dt: 07/01/2026.**

#### **CIRCULAR**

This is to inform all ECE Department BoS members that the 3rd Board of Studies (BoS) meeting will be held on Friday, January 9, 2026, at 10:00 AM via online mode (Zoom) from the MPMC Lab. You are all cordially invited to attend; the meeting link will be shared via email.

#### **Agenda**

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair

**Head of the Department & BoS Chairman**

*Head

Department of ECE

D.N.R. College of Engg. & Tech

BHIMAVARAM-534 202.*

#### **Copy To:**

1. The Members of the BoS

2. The Principal

3. The Dean (Academics)

4. To the Office File

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with 'A+' Grade by NAAC & Accredited by NBA (B. TECH - CSE, ECE & EEE)

Ph: 08816-221238 Email: [dncol@gmail.com](mailto:dncol@gmail.com) website: <https://dnrest.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

Bhimavaram,

Dt: 07/01/2026.

**Dr. B. T Krishna,

Professor, ECE Department,

University College of Engineering,

Kakinada, AP-533003.**

Dear sir,

**Sub: DNR College of Engineering & Technology, ECE Dept-Board of Studies Meeting-Reg.**

We take the privilege in inviting you for the Board of Studies (BoS) 3<sup>rd</sup> meeting of the ECE department, DNR College of Engineering & Technology(9P) as a Subject Expert from outside the parent university. It is proposed to discuss and finalize the following for the A.Y. 2026- 27.

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair

In this regard, you are requested to attend the on-line meeting scheduled to be held on 09/01/2026, Friday at 10:00 AM in the MPMC Lab, ECE Department. The link will be shared through mail or WhatsApp.

Kindly accept our invitation and make it convenient to attend the Board of Studies meeting.

**Yours Sincerely,**

(Dr. K. Venu Gopal)

**HoD and Chairman BoS.**

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH - CSE, ECE & EEE)

Ph: 08816-221238 Email: [dncet@gmail.com](mailto:dncet@gmail.com) website: <https://dncet.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

Bhimavaram,

Dt: 07/01/2026.

To

Dr. N. Udaya Kumar,

Professor, ECE Department,

SRKR Engg. College (Autonomous),

Bhimavaram, AP-534202.

Dear Sir,

**Sub: DNR College of Engineering & Technology, ECE Dept-Board of Studies Meeting-Reg.**

We take the privilege in inviting you for the Board of Studies (BoS) 3<sup>rd</sup> meeting of the ECE department, DNR College of Engineering & Technology(9P) as a Subject Expert from outside the parent university. It is proposed to discuss and finalize the following for the A.Y. 2026-27.

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair.

In this regard, you are requested to attend the on-line meeting scheduled to be held on 09/01/2026, Friday at 10:00 AM in the MPMC Lab, ECE Department. The link will be shared through mail or WhatsApp.

Kindly accept our invitation and make it convenient to attend the Board of Studies meeting.

Yours Sincerely,

(Dr. K. Venu Gopal),

HoD and Chairman BoS.

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [drect@gmail.com](mailto:drect@gmail.com) website: <https://dnrect.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

Bhimavaram,

Dt: 07/01/2026.

To

**Dr. P. Srinivasa Rao,

Assoc. Professor, ECE Department,

St. Anna's College of Engineering & Technology (Autonomous),

Chirala, AP – 523187.**

Dear sir,

**Sub: DNR College of Engineering & Technology, ECE Dept-Board of Studies Meeting-Reg.**

We take the privilege in inviting you for the Board of Studies (BoS) 3<sup>rd</sup> meeting of the ECE department, DNR College of Engineering & Technology(9P) as a Subject Expert from outside the parent university. It is proposed to discuss and finalize the following for the A.Y. 2026- 27.

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair.

In this regard, you are requested to attend the on-line meeting scheduled to be held on 09/01/2026, Friday at 10:00 AM in the MPMC Lab, ECE Department. The link will be shared through mail or WhatsApp.

Kindly accept our invitation and make it convenient to attend the Board of Studies meeting.

Yours Sincerely,

(Dr. K. Venu Gopal),

HoD and Chairman BoS.

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNPUK, Kakulunda

Credited with 'A'' Grade by NAAC & Accredited by NBA (B. TECH - CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnceet@gmail.com](mailto:dnceet@gmail.com) website: <http://dnceet.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

**Bhimavaram,

Dt: 07/01/2026.**

**Mrs. I. Pavani,

2016-20 Batch,

Roll No.169P1A0416,

Bhimavaram,

AP-534202.**

**Dear sir,**

**Sub: DNR College of Engineering & Technology, ECE Dept-Board of Studies Meeting-Reg.**

We take the privilege in inviting you for the Board of Studies (BoS) 3<sup>rd</sup> meeting of the ECE department, DNR College of Engineering & Technology(9P) as a Subject Expert from outside the parent university. It is proposed to discuss and finalize the following for the A.Y. 2026- 27.

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair.

In this regard, you are requested to attend the on-line meeting scheduled to be held on 09/01/2026, Friday at 10:00 AM in the MPMC Lab, ECE Department. The link will be shared through mail or WhatsApp.

Kindly accept our invitation and make it convenient to attend the Board of Studies meeting.

**Yours Sincerely,**

*K Venu Gopal*

(Dr. K. Venu Gopal)

**HoD and Chairman BoS.**

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH - CSE, ECE & EEE)

Ph: 08816-221238 Email: dnrce@gmail.com website: <https://dnrect.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

Bhimavaram,

Dt: 07/01/2026.

Mr. Sriramulu Govada,

Design. Technical Officer 'A',

DRDO, Visakhapatnam,

AP-530027.

Dear sir,

**Sub: DNR College of Engineering & Technology, ECE Dept-Board of Studies Meeting-Reg.**

We take the privilege in inviting you for the Board of Studies (BoS) 3<sup>rd</sup> meeting of the ECE department, DNR College of Engineering & Technology(9P) as a Subject Expert from outside the parent university. It is proposed to discuss and finalize the following for the A.Y. 2026- 27.

1. Welcome Speech by the Chairperson.

2. Introducing the members of the Board of Studies.

3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.

4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.

6. Finalization of Model Question Papers and List of Paper Setters.

7. Any other item with the permission of the chair

In this regard, you are requested to attend the on-line meeting scheduled to be held on 09/01/2026, Friday at 10:00 AM in the MPMC Lab, ECE Department. The link will be shared through mail or WhatsApp.

Kindly accept our invitation and make it convenient to attend the Board of Studies meeting.

Yours Sincerely,

(Dr. K. Venu Gopal)

HoD and Chairman BoS.

ECE DEPARTMENT ECE &lt;dnrctece@gmail.com&gt;

**Invitation to the 3rd Board of Studies (BoS) Meeting – ECE Department, DNR CET**

1 message

ELECTRONICS &lt;dnrctece@gmail.com&gt;

To: tkbattula@jntucek.ac.in

Thu, Jan 8, 2026 at 12:59 PM

Respected sir ,

Greetings from the Department of Electronics and Communication Engineering, DNR College of Engineering and Technology!

On behalf of the ECE Department, we are pleased to cordially invite you to attend the 3rd Board of Studies (BoS) Meeting of our department. Your valuable presence and insights will greatly contribute to our academic discussions and curriculum development.

--

With Warm regards

HOD

Dept. of ECE

DNR CET

Bhimavaram, W.G.Dist.,

A.P-534202.

Dr.B.T Krishna.pdf

364K

ECE DEPARTMENT ECE &lt;dnrcetece@gmail.com&gt;

**Invitation to the 3rd Board of Studies (BoS) Meeting – ECE Department, DNR CET**

2 messages

**ELECTRONICS** <dnrcetece@gmail.com>

To: Uday N <udayvas2005@gmail.com>

Thu, Jan 8, 2026 at 12:58 PM

Respected sir ,

Greetings from the Department of Electronics and Communication Engineering, DNR College of Engineering and Technology!

On behalf of the ECE Department, we are pleased to cordially invite you to attend the 3rd Board of Studies (BoS) Meeting of our department. Your valuable presence and insights will greatly contribute to our academic discussions and curriculum development.

--

With Warm regards

HOD

Dept. of ECE

DNR CET

Bhimavaram, W.G.Dist.,

A.P-534202.

Dr.N.Uday Kumar.pdf

345K

**Uday N** <udayvas2005@gmail.com>

To: ELECTRONICS <dnrcetece@gmail.com>

Thu, Jan 8, 2026 at 4:23 PM

Ok sir.

All the best sir

with best wishes and regards

Dr. N. Udaya Kumar M. Tech, Ph. D, MISTE, MSOI, MBMESI, MSEMC(EI), FIE, FIETE

Senior Member IEEE(SMIEEE),

Professor and Head, Department of ECE,

SRKR Engineering College,

Bhimavaram

Ex-Secretary, IEEE Comsoc/SP Societies Joint Chapter, IEEE Vizag Bay Section

Ex-AP State Committee Member (IE)- ET Division

Mobile: 9440354093(Whatsapp)

:6300465439(Whatsapp)

[Quoted text hidden]

ECE DEPARTMENT ECE &lt;dnrcetece@gmail.com&gt;

**Invitation to the 3rd Board of Studies (BoS) Meeting – ECE Department, DNRCET**

1 message

**ELECTRONICS** <dnrcetece@gmail.com>

To: Srinivas Rao <psraoece@gmail.com>

Thu, Jan 8, 2026 at 12:55 PM

Respected sir ,

Greetings from the Department of Electronics and Communication

Engineering, DNR College of Engineering and Technology!On behalf of the ECE Department, we are pleased to cordially invite

you to attend the 3rd Board of Studies (BoS) Meeting of our

department. Your valuable presence and insights will greatly

contribute to our academic discussions and curriculum development.

--

With Warm regards

HoD

Dept. of ECE

DNRCET

Bhimavaram, W.G.Dist.,

A.P-534202.

**Dr.P.Srinivasa Rao.pdf**

374K

ECE DEPARTMENT ECE &lt;dnrcetece@gmail.com&gt;

**Invitation to the 3rd Board of Studies (BoS) Meeting – ECE Department, DNR CET**

1 message

**ELECTRONICS** <dnrcetece@gmail.com>

To: Sriram Govada <sriramgovada@gmail.com>

Thu, Jan 8, 2026 at 1:01 PM

Respected sir ,

Greetings from the Department of Electronics and Communication

Engineering, DNR College of Engineering and Technology!

On behalf of the ECE Department, we are pleased to cordially invite

you to attend the 3rd Board of Studies (BoS) Meeting of our

department. Your valuable presence and insights will greatly

contribute to our academic discussions and curriculum development.

—

With Warm regards

HOD

Dept. of ECE

DNR CET

Bhimavaram, W.G.Dist.,

A.P-534202.

---

**Mr.Sriamulu Govada.pdf**

352K

ECE DEPARTMENT ECE <dnrcetece@gmail.com>

## Invitation to the 3rd Board of Studies (BoS) Meeting – ECE Department, DNRCET

ELECTRONICS <dnrcetece@gmail.com>

To: Pavani Indukuri <pavaniindukuri123@gmail.com>

Thu, Jan 8, 2026 at 1:01 PM

Respected sir ,

Greetings from the Department of Electronics and Communication

Engineering, DNR College of Engineering and Technology!

On behalf of the ECE Department, we are pleased to cordially invite

you to attend the 3rd Board of Studies (BoS) Meeting of our

department. Your valuable presence and insights will greatly

contribute to our academic discussions and curriculum development.

—

With Warm regards

HOD

Dept. of ECE

DNRCET

Bhimavaram, W.G.Dist.,

A.P-534202.

---

I.Pavani.pdf

398K

## **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)**

**Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A+ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>**

### **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

**Bhimavaram,

09/01/2026.**

Ref: DNRCET/ECED/2025-26/BOS-MOM/1

#### **Minutes of Meeting (MOM) of the Board of Studies (BOS)**

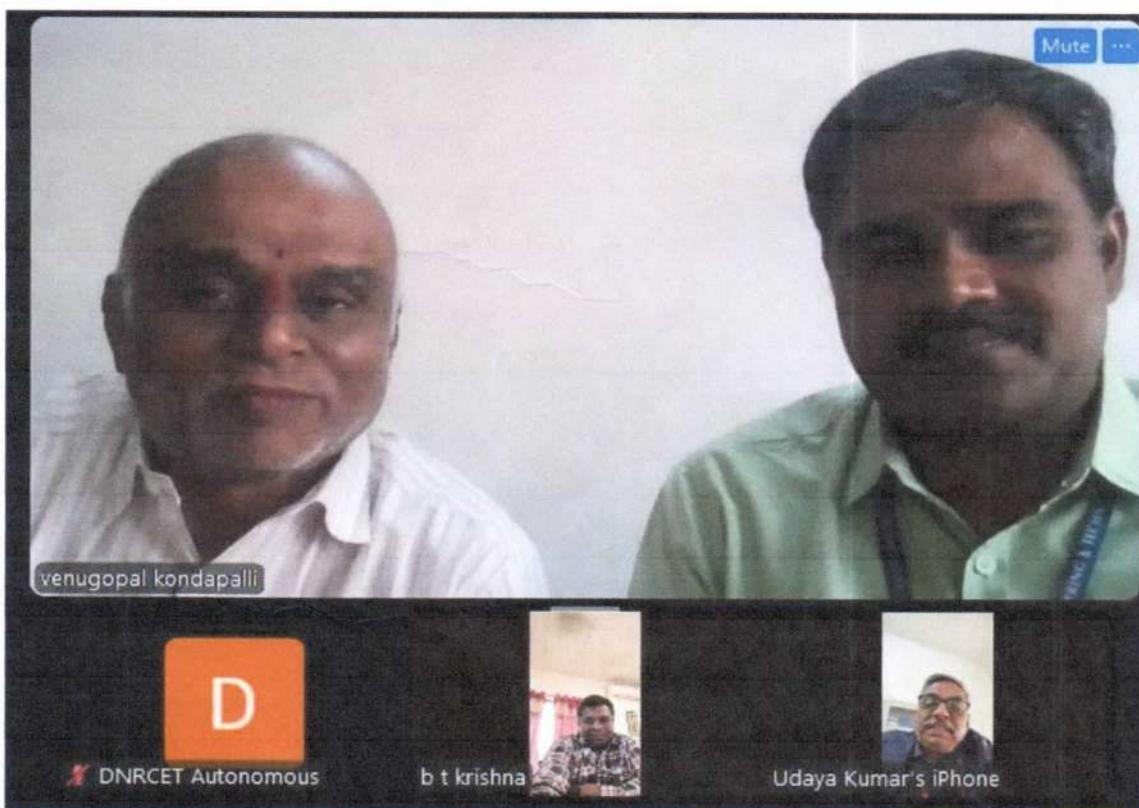

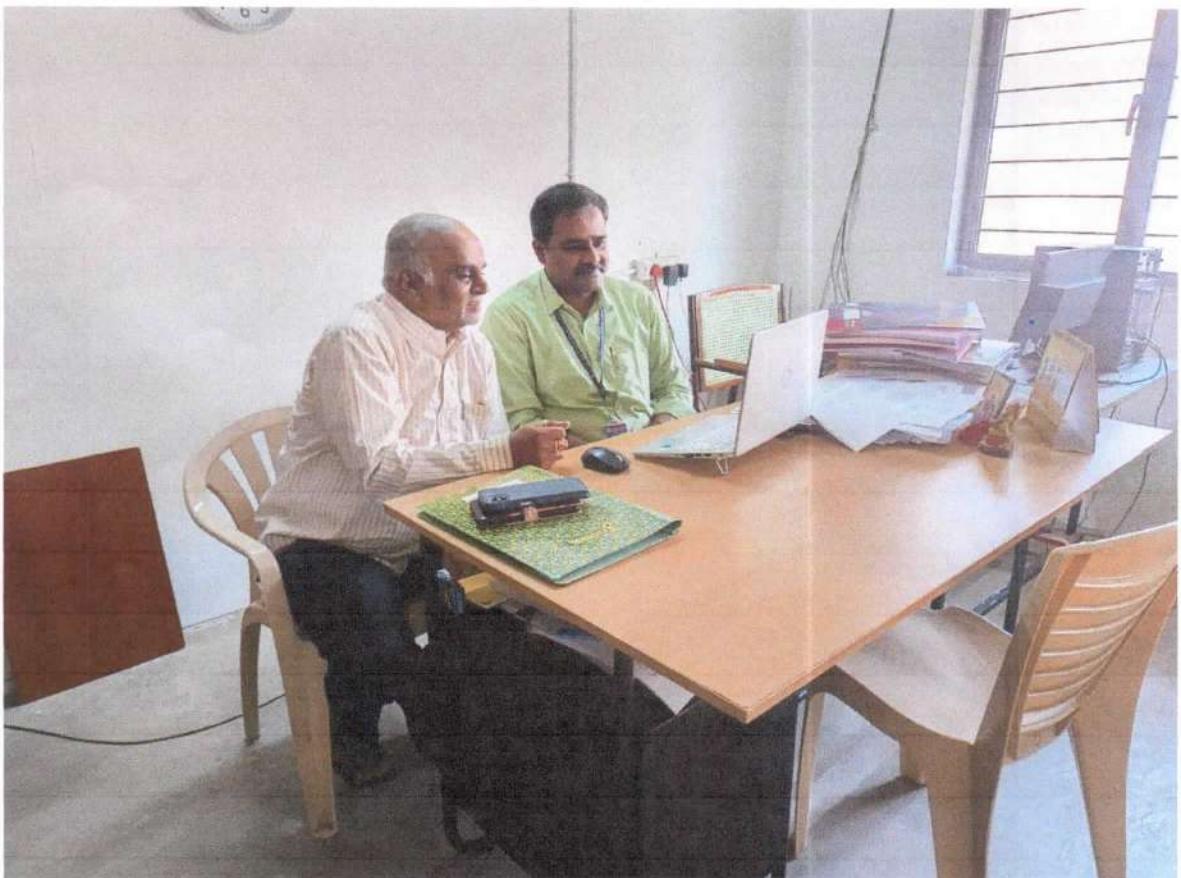

The 3rd Board of Studies (BoS) meeting for the Electronics & Communication Engineering (ECE) Department took place on Friday, January 9, 2026, via Zoom in the MPMC Lab. The session focused on reviewing the proposed agenda and adopting key resolutions.

#### **Meeting link**

[https://us06web.zoom.us/j/88650471236?pwd=sozL2jB9kdnblbXv6n0XF4t6oGuzel.](https://us06web.zoom.us/j/88650471236?pwd=sozL2jB9kdnblbXv6n0XF4t6oGuzel)

#### **Agenda:**

- 1. Welcome Speech by the Chairperson.**

- 2. Introducing the members of the Board of Studies.**

- 3. To discuss and finalize the proposed III B. Tech. I & II Semester Course structure and Syllabus of DR24 Regulations.**

- 4. To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.**

- 5. Ratification of Course Objectives and Course Outcomes for the proposed Curriculum.**

- 6. Finalization of Model Question Papers and List of Paper Setters.**

- 7. Any other item with the permission of the chair**

The following members attended the meeting:

| <b>Name(s) of the Member(s)/Nominee(s)</b>                                                                                                                                                                              | <b>Designation in Committee</b> | <b>Signature</b>                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------|

| Dr. K. Venu Gopal                                                                                                                                                                                                       | Chairperson                     |  |

| Dr. B. T Krishna,<br>Professor, ECE Department,<br>University College of<br>Engineering,<br>Kakinada, AP-533003.<br>e-mail: <a href="mailto:tkbattula@jntucek.ac.in">tkbattula@jntucek.ac.in</a><br>Mobile: 9502770755. | Member<br>(University Nominee)  | Attended<br>ONLINE                                                                    |

## D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

|                                                                                                                                                                                                 |                                                                                      |                    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|--------------------|

| Dr. N. Udaya Kumar,<br>Professor, ECE Dept,<br>SRKR Engineering. College<br>(Autonomous),<br>Bhimavaram-534202,<br>e-mail: nuk@srkrec.ac.in<br>Mobile: 9440354093.                              | <b>Member</b><br><b>(Subject experts from<br/>outside the parent<br/>University)</b> | Attended<br>ONLINE |

| Dr. P. Srinivasa Rao,<br>Assoc. Professor, ECE Dept.,<br>St. Anna's College of<br>Engineering & Technology<br>(Autonomous), Chirala-523187<br>e-mail: psraoece@gmail.com<br>Mobile: 6281266754. | <b>Member</b><br><b>(Subject experts from<br/>outside the parent<br/>University)</b> | Attended<br>ONLINE |

| Mr. Sriramulu Govada,<br>Design. Technical Officer 'A',<br>DRDO, Visakhapatnam,<br>e-mail:<br>sriramgovada@gmail.com<br>Mobile: 9492126360.                                                     | <b>Member</b><br><b>(Industrial Expert)</b>                                          | Attended<br>ONLINE |

| Mrs. I. Pavani,<br>2016-20 Batch,<br>Roll No.169P1A0416,<br>e-mail:<br>pavaniindukuri123@gmail.com,<br>Mobile No: 63039 84842.                                                                  | <b>Member</b><br><b>(College alumni)</b>                                             | Attended<br>ONLINE |

| Dr. Nekkanti Venkata Rao                                                                                                                                                                        | <b>Members<br/>of the Department</b>                                                 | ✓                  |

| Dr A. Purna Ramesh                                                                                                                                                                              |                                                                                      | ✓                  |

| Dr. S. Ravi chandh                                                                                                                                                                              |                                                                                      | ✓                  |

| Mr. Kopalli Venkanna Naidu                                                                                                                                                                      |                                                                                      | ✓                  |

| Mr. Kurma Sekhar Babu                                                                                                                                                                           |                                                                                      | ✓                  |

| Mrs.N.S.V.L. Sowjanya                                                                                                                                                                           |                                                                                      | ✓                  |

## D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A+ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

|                             |  |                                                                                       |

|-----------------------------|--|---------------------------------------------------------------------------------------|

| Mr. K. Satish Kumar         |  |    |

| Mrs. N Mary Leena           |  |    |

| Mr. M. Venu                 |  |    |

| Mr. S. Apparao              |  |    |

| Mrs. K. Indira Priyadarsini |  |    |

| Mrs. B. Nagamani            |  |    |

| Mr. P. Gopala Swami         |  |    |

| Mrs. K. Krishna Deepika     |  |    |

| Mrs. P. Srivalli            |  |  |

| Mr. Vendra Bhavani Durga    |  |  |

| Mrs. K. Durga               |  |  |

| Mrs. U. Sai Mounica         |  |  |

| Mr. S. Joseph               |  |  |

| Mrs. P. Pardhavi            |  |  |

| Mr. P. Narasimha Murthy     |  |  |

| Mr. V. Phani Kiran          |  |  |

| Ms. N. Sowjanya             |  |  |

| Ms. K. Uma devi             |  |  |

| Mr. G. Manikanta            |  |  |

| Mr. T. Srinivas             |  |  |

| Mr. J. S. S. Ramaraju       |  |  |

| Ms. S. R. S. Anusha         |  |  |

| Ms. G. Chinnari             |  |  |

## **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### **DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

---

The Principal of DNRCET opened the meeting by thanking the university nominee and all BoS members. Dr. K. Venu Gopal, Chairman of the ECE BoS, then took charge of the proceedings. The meeting concluded with the following key resolutions:

**Resolutions:**

**Agenda Point 1:** Welcome speech by the chairperson

**Resolution:** Dr. K. Venu Gopal, Chairman of the BoS, warmly welcomed all BoS members.

**Agenda Point 2:** Introduction of members

**Resolution:** The Chairman of BoS, Dr. K. Venu Gopal, welcomed all the members and introduced internal BoS members to external BoS members.

The meeting began with the III B. Tech curriculum presentation for semesters I & II.

**Agenda Point 3:** To discuss and finalize the proposed III B. Tech-I & II Semester ECE (Theory and Lab) courses of DR24 Regulations.

**Resolution:** After clearly discussing every unit of theory courses

III B. Tech-I Semester DR24 Syllabus (Theory & Labs)- including professional Electives courses

1. Analog & Digital IC Applications, 2. Digital communications, 3. Antennas and Wave Propagation, 4. Digital System Design through HDL, 5. Optical Communications, 6. Electronic Measurements and Instrumentation, 7. Computer Organization and Architecture, 8. Analog & Digital IC Applications Lab, 9. Analog and digital communications Lab, 10. Applications of Lab view for Instrumentation & Communications, 11. Design of PCB & Antennas Lab.

III B. Tech-II Semester DR24 Syllabus (Theory & Labs)- including professional Electives courses

1. VLSI Design, 2. Microprocessors & Microcontrollers, 3. Digital Signal Processing, 4. Analog IC Design, 5. Satellite Communication, 6. Smart and Wireless Instrumentation, 7. Machine Learning, 8. Bio Medical Instrumentation, 9. Microwave Engineering, 10. Embedded Systems, 11. Artificial Intelligence, 12. VLSI Design Lab, 13. Microprocessors & Microcontrollers Lab, 14. Machine Learning Lab

**List of Open Elective courses offered by department of ECE:**

Pool 1: Open Elective 1 (Either of the 4 subjects)-

1. Electronic Devices and Circuits, 2. Signals and Systems, 3. Probability Theory and Random Variables, 4. Network Analysis

Pool 2: Open Elective 2 (Either of the 4 subjects)-

1. Linear and Digital IC Applications, 2. Principles of Communications, 3. Principles of Signal Processing, 4. Microprocessors & Microcontrollers.

Pool 3: Open Elective 3 (Either of the 4 subjects)-

1. Fundamentals of VLSI Design, 2. Digital Electronics, 3. Electronic Measurements and Instrumentations, 4. Optical Communications.

Pool 4: Open Elective 4 (Either of the 4 subjects)-

1. Principles of Cellular & Mobile Communications, 2. Fundamentals of Satellite Communications, 3. Embedded Systems, 4. Transducers and Signal Conditioning.

**Annexure-A (Enclosed Annexure-A).**

## D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

**Agenda Point 4:** To discuss and finalize the proposed M. Tech. Course structure and Syllabus of DR25 Regulations.

**Resolution:** After clearly discussing every unit of theory courses,

**M. Tech DR25 I Semester Syllabus (Theory & labs)-1.** including professional Electives courses 1.Mathematical Foundation for Communication Engineering, 2. Digital System Design, 3. Wireless Communications & Networks, 4. Software Defined Radio, 5. Optical Communication & Networks, 6. Radio and Navigational Aids, 7. FPGA and ASIC Design, 8. System Design with RTOS & Embedded LINUX, 9. System Design Using Verilog, 10. Digital System Design Laboratory, 11. Wireless Communications Laboratory, 12. Seminar.

**M. Tech DR25 II Semester Syllabus (Theory & labs)-1.** including professional Electives courses 1.Information Theory and Coding, 2. IoT & its Communication Protocols, 3. Embedded System Design, 4. Design for Testability, 5. MEMS, 6. System on Chip Design, 7. Detection and Estimation Theory, 8. EMI/ EMC, 9. ARM Controllers and Embedded C, 10. Internet of Things Lab, 11. Embedded System Design Lab, 12. Seminar.

**M. Tech DR25 III & IV Semester Syllabus (Theory & labs)-1.** Research Methodology and IPR/Swayam 12-week MOOC course – RM & IPR, 2. Summer Internship / Industrial Training, 3. Comprehensive Viva, 8. Project Work (Dissertation Part – A ).

**IV Semester Syllabus (Theory & labs)**

I,Project Work (Dissertation Part – B)

Other Branches Subjects: 1. Vision Systems and Image Processing.

**II. Annexure-B (Enclosed Annexure -B).**

**Agenda Point- 5:** Ratification of Course Objectives and Course Outcomes for the proposed subjects.

**Resolution:** Following detailed discussions, the BoS approved the proposed Course Objectives and Outcomes, incorporating the modifications made to the theory courses and labs outlined in agenda items 3 and 4.

**Agenda Point- 6:** Finalization of Model Paper.

**Resolution:** The BoS members recommended aligning Course Outcomes (COs) with the sequence of exam questions, replacing Knowledge Level (KL) with Bloom's Taxonomy Level (BL), and assigning 4 or 6 marks to select long-answer questions (out of 10). Following confirmation of the COs, BL levels, and marking scheme, the BoS approved the proposed model question papers for external theory course examinations. Annexure-C (**Enclosed Annexure -C**).

**Agenda Point 7:** Any other item with the permission of the chair.

**Resolution:** The Chairman of the Board of Studies emphasized the importance of MOOCs and SWAYAM/NPTEL courses for enhancing student skills. He also outlined honors and minor courses, aligned with APSCHE and JNTUK Kakinada guidelines

In conclusion, the Chairman summarized the agenda and resolutions, extended a vote of thanks, and appreciated every member's cooperative effort

Note: All conversations from the BoS meetings are captured on the Zoom platform and kept in the Department's records.

Chairman, BoS

## D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY (AUTONOMOUS)

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

Bhimavaram,

09/01/2026.

Ref: DNRCET/ECED/2026-27/BOS-photos/1

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

(AUTONOMOUS)**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

**DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING**

*Keval Goel*

Chairman, BoS

# **Annexure-A**

**DR24**

**B.Tech**

**Course Structure**

**&**

**Syllabus**

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING

### B.Tech. III Year I Semester

| S.No.        | Category | Title                                                                                                                                                            | Course Code                                              | L         | T        | P         | C         |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|----------|-----------|-----------|

| 1            | PC       | Analog & Digital IC Applications                                                                                                                                 | BT24EC3101                                               | 3         | 0        | 0         | 3         |

| 2            | PC       | Digital communications                                                                                                                                           | BT24EC3102                                               | 3         | 0        | 0         | 3         |

| 3            | PC       | Antennas and Wave Propagation                                                                                                                                    | BT24EC3103                                               | 3         | 0        | 0         | 3         |

| 4            | PE-I     | 1. Digital System Design through HDL<br>2. Optical Communications<br>3. Electronic Measurements and Instrumentation<br>4. Computer Organization and Architecture | BT24EC31P1A<br>BT24EC31P1B<br>BT24EC31P1C<br>BT24EC31P1D |           |          |           |           |

| 5            | OE-I     | OR<br>Entrepreneurship Development & Venture Creation                                                                                                            | BT24HS3101                                               | 3         | 0        | 0         | 3         |

| 6            | PC       | Analog & Digital IC Applications Lab                                                                                                                             | BT24EC3104                                               | 0         | 0        | 3         | 1.5       |

| 7            | PC       | Analog and digital communications Lab                                                                                                                            | BT24EC3105                                               | 0         | 0        | 3         | 1.5       |

| 8            | SEC      | Applications of Lab view for Instrumentation & Communications                                                                                                    | BT24EC3106                                               | 0         | 1        | 2         | 2         |

| 9            | ES       | Design of PCB & Antennas Lab                                                                                                                                     | BT24EC3107                                               | 0         | 0        | 2         | 1         |

| 10           |          | Evaluation of Community Service Internship                                                                                                                       | BT24BS3103                                               | -         | -        | -         | 2         |

| <b>Total</b> |          |                                                                                                                                                                  |                                                          | <b>15</b> | <b>1</b> | <b>10</b> | <b>23</b> |

|    |                                                                         |   |   |   |     |

|----|-------------------------------------------------------------------------|---|---|---|-----|

| MC | Minor Course (Student may select from the same specialized minors pool) | 3 | 0 | 3 | 4.5 |

| MC | Minor Course through SWAYAM / NPTEL (Minimum 12 Week, 3 credit course)  | 3 | 0 | 0 | 3   |

| HC | Honors Course (Student may select from the same Honors pool)            | 3 | 0 | 0 | 3   |

| HC | Honors Course (Student may select from the same Honors Pool)            | 3 | 0 | 0 | 3   |

**K. Venkateswara Rao**

**Head**

**Department of ECE**

**D.N.R. College of Engg. & Tech**

**BHIMAVARAM-534 207**

**D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

**B.Tech. III Year II Semester**

| S.No.        | Category | Title                                                                                                                | Course Code                                              | L         | T        | P         | C         |

|--------------|----------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|-----------|----------|-----------|-----------|

| 1            | PC       | VLSI Design                                                                                                          | BT24EC3201                                               | 3         | 0        | 0         | 3         |

| 2            | PC       | Microprocessors & Microcontrollers                                                                                   | BT24EC3202                                               | 3         | 0        | 0         | 3         |

| 3            | PC       | Digital Signal Processing                                                                                            | BT24EC3203                                               | 3         | 0        | 0         | 3         |

| 4            | PE-II    | 1. Analog IC Design<br>2. Satellite Communication<br>3. Smart and Wireless<br>Instrumentation<br>4. Machine Learning | BT24EC32P2A<br>BT24EC32P2B<br>BT24EC32P2C<br>BT24EC32P2D | 3         | 0        | 0         | 3         |

| 5            | PE-III   | 1. Bio Medical Instrumentation<br>2. Microwave Engineering<br>3. Embedded Systems<br>4. Artificial Intelligence      | BT24EC32P3A<br>BT24EC32P3B<br>BT24EC32P3C<br>BT24EC32P3D | 3         | 0        | 0         | 3         |

| 6            | OE-II    | Open Elective from Another Department                                                                                |                                                          | 3         | 0        | 0         | 3         |

| 7            | PC       | VLSI Design Lab                                                                                                      | BT24EC3204                                               | 0         | 0        | 3         | 1.5       |

| 8            | PC       | Microprocessors & Microcontrollers Lab                                                                               | BT24EC3205                                               | 0         | 0        | 3         | 1.5       |

| 9            | SEC      | Machine Learning Lab                                                                                                 | BT24EC3206                                               | 0         | 1        | 2         | 2         |

| 10           | AC       | Research Methodology and IPR                                                                                         | BT24HS3201                                               | 2         | 0        | 0         | -         |

| <b>Total</b> |          |                                                                                                                      |                                                          | <b>20</b> | <b>1</b> | <b>08</b> | <b>23</b> |

Mandatory Industry Internship of 08 weeks duration during summer vacation

|    |                                                                            |   |   |   |     |

|----|----------------------------------------------------------------------------|---|---|---|-----|

| MC | Student may select from the same minor's pool                              | 3 | 0 | 3 | 4.5 |

| MC | Minor Course<br>(Student may select from the same specialized minors pool) | 3 | 0 | 0 | 3   |

| HC | Student may select from the same honors pool                               | 3 | 0 | 0 | 3   |

| HC | Honors Course (Student may select from the honors pool)                    | 3 | 0 | 0 | 3   |

**Head**

**Department of ECE**

**D.N.R. College of Engg. & Tech**

**BHIMAVARAM-534 202.**

# **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

---

## **List of Open Elective courses offered by department of ECE:**

### **Pool 1: Open Elective 1 (Either of the 4 subjects)**

|                                            |               |

|--------------------------------------------|---------------|

| 1. Electronic Devices and Circuits         | - BT24EC31O1A |

| 2. Signals and Systems                     | - BT24EC31O1B |

| 3. Probability Theory and Random Variables | - BT24EC31O1C |

| 4. Network Analysis                        | - BT24EC31O1D |

### **Pool 2: Open Elective 2 (Either of the 4 subjects)**

|                                       |               |

|---------------------------------------|---------------|

| 1. Linear and Digital IC Applications | - BT24EC32O2A |

| 2. Principles of Communications       | - BT24EC32O2B |

| 3. Principles of Signal Processing    | - BT24EC32O2C |

| 4. Microprocessors & Microcontrollers | - BT24EC32O2D |

### **Pool 3: Open Elective 3 (Either of the 4 subjects)**

|                                                 |               |

|-------------------------------------------------|---------------|

| 1. Fundamentals of VLSI Design                  | -BT24EC41O3A  |

| 2. Digital Electronics                          | - BT24EC41O3B |

| 3. Electronic Measurements and Instrumentations | - BT24EC41O3C |

| 4. Optical Communications                       | - BT24EC41O3D |

### **Pool 4: Open Elective 4 (Either of the 4 subjects)**

|                                                   |               |

|---------------------------------------------------|---------------|

| 1. Principles of Cellular & Mobile Communications | - BT24EC41O4A |

| 2. Fundamentals of Satellite Communications       | - BT24EC41O4B |

| 3. Embedded Systems                               | - BT24EC41O4C |

| 4. Transducers and Signal Conditioning            | - BT24EC41O4D |

*K Venu Gopal*

**Head**

**Department of ECE**

**D.N.R. College of Engg. & Tech**

**BHIMAVARAM-534 207**

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

|                            |                                                                    |          |          |          |          |

|----------------------------|--------------------------------------------------------------------|----------|----------|----------|----------|

| <b>III Year-I Semester</b> | <b>ANALOG &amp; DIGITAL IC APPLICATIONS</b><br><b>(BT24EC3101)</b> | <b>L</b> | <b>T</b> | <b>P</b> | <b>C</b> |

|                            |                                                                    | <b>3</b> | <b>0</b> | <b>0</b> | <b>3</b> |

### Course Outcomes:

- Apply the operational principles and characteristics of op-amps to design and analyze analog circuits such as amplifiers and active filters.

- Design waveform generators and comparator circuits using op-amps for signal processing applications.

- To understand the concept of digital- to-analog, analog-to-digital circuit and its operation.

- Compare different data conversion techniques (DAC and ADC) and implement digital-to-analog and analog-to-digital conversion circuits in real-time applications.

- Implement and troubleshoot combinational and sequential logic circuits using digital ICs.

- Design and interface digital systems using programmable logic devices like PLDs and FPGAs.

**CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)**

|            | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| <b>CO1</b> | 2   | 2   | 3   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | -    |

| <b>CO2</b> | 3   | 2   | 3   | -   | -   | -   | -   | -   | -   | -    | -    | 2    | 2    | -    |

| <b>CO3</b> | 3   | 3   | 2   | 1   | -   | -   | -   | -   | -   | -    | -    | 2    | 2    | 2    |

| <b>CO4</b> | 3   | 3   | -   | 1   | -   | -   | -   | -   | -   | -    | -    | 2    | 2    | 2    |

| <b>CO5</b> | 3   | 2   | 1   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| <b>CO6</b> | 3   | 2   | 3   | 1   | -   | -   | -   | -   | -   | -    | -    | 2    | 2    | -    |

### UNIT-I

**Operational Amplifier:** Ideal and Practical Op-Amp, Op-Amp Characteristics, DC and AC Characteristics, features of 741 Op-Amp, Modes of Operation-Inverting, Non-Inverting, Differential, Instrumentation Amplifier, AC Amplifier, Differentiators and Integrators, Comparators, Schmitt Trigger, Introduction to Voltage Regulators, Features of 723 Regulator, Three Terminal Voltage Regulators.

### UNIT-II

**Op-Amp, IC-555 & IC565 Applications:** Introduction to Active Filters, Characteristics of Band pass, Band reject and All Pass Filters, Analysis of 1<sup>st</sup> order LPF & HPF Butterworth Filters, Waveform Generators – Triangular, Sawtooth, Square Wave, IC555 Timer-Functional Diagram, Monostable and Astable Operations, Applications, IC565 PLL-Block Schematic, principle and Applications.

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## UNIT-III

**Data Converters:** Introduction, Basic DAC techniques, Different types of DACs-Weighted resistor DAC, R-2R ladder DAC, Inverted R-2R DAC, Different Types of ADCs – Parallel Comparator Type ADC, Counter Type ADC, Successive Approximation ADC and Dual Slope ADC, DAC and ADC Specifications.

## UNIT-IV

**Combinational Logic ICs:** Specifications and Applications of TTL-74XX & CMOS 40XX Series ICs - Code Converters, Decoders, LED & LCD Decoders with Drivers, Encoders, Priority Encoders, Multiplexers, De-multiplexers, Priority Generators/Checkers, Parallel Binary Adder/Subtractor, Magnitude Comparators.

## UNIT-V

**Sequential Logic IC's and Memories:** Familiarity with commonly available 74XX & CMOS40XX Series ICs - All Types of Flip-flops, Synchronous Counters, Decade Counters, Shift Registers.

Memories - ROM Architecture, Types of ROMS & Applications, RAM Architecture, Static & Dynamic RAMs.

## TEXTBOOKS:

1. Ramakanth A. Gayakwad-Op-Amps & Linear ICs, PHI, 2003.

2. Floyd and Jain-Digital Fundamentals, 8<sup>th</sup> Ed., Pearson Education, 2005.

## REFERENCE BOOKS:

1. D. Roy Chowdhury-Linear Integrated Circuits, New Age International(p) Ltd, 2<sup>nd</sup> Ed., 2003.

2. John F. Wakerly-Digital Design Principles and Practices, 3<sup>rd</sup> Ed., Pearson, 2009.

3. Salivahana-Linear Integrated Circuits and Applications, TMH, 2008.

4. William D. Stanley-Operational Amplifiers with Linear Integrated Circuits, 4<sup>th</sup> Ed., Pearson Education India, 2009.

## e-Resources: -

- <https://epgp.inflibnet.ac.in>

- [NPTEL Linear ICs, TI Op-Amp Handbook](https://nptel.ac.in/courses/101/101/101010101/)

- [https://mrcet.com/downloads/digital\\_notes/EEE/13092021/LINEAR%20%26%20DIGITAL%20IC.pdf](https://mrcet.com/downloads/digital_notes/EEE/13092021/LINEAR%20%26%20DIGITAL%20IC.pdf)

*Shivu Gopal*

Head

Department of ECE

D.N.R. College of Engg. & Tech

BHIMAVARAM-534 207

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

|                            |                                                      |          |          |          |          |

|----------------------------|------------------------------------------------------|----------|----------|----------|----------|

| <b>III Year-I Semester</b> | <b>DIGITAL COMMUNICATIONS</b><br><b>(BT24EC3102)</b> | <b>L</b> | <b>T</b> | <b>P</b> | <b>C</b> |

|                            |                                                      | <b>3</b> | <b>0</b> | <b>0</b> | <b>3</b> |

### **Course Outcomes:**

- To Describe basic components of Digital Communication Systems and to determine the performance of different pulse digital modulation techniques.

- To determine the performance of digital modulation techniques for the generation and digital representation of the signals.

- To design optimum receiver for Digital Modulation techniques and to determine the probability of error for various digital modulation schemes.

- To analyze baseband receivers and design optimum receivers using matched filter concepts, and to evaluate the probability of error for coherent and non-coherent digital detection schemes.

- To compute and analyze error detecting and error correction codes block codes, cyclic codes.

- To compute and analyze convolution codes and Turbo codes.

**CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)**

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

| CO2 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 2    |

| CO3 | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| CO4 | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| CO5 | 3   | 3   | 2   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 1    |

| CO6 | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 2    | 2    | 2    |

### **UNIT I**

**PULSE DIGITAL MODULATION:** Elements of digital communication systems, advantages of digital communication systems, Elements of PCM: Sampling, Quantization & Coding, Quantization error, Companding in PCM systems. Differential PCM systems (DPCM). Delta modulation, its draw backs, adaptive delta modulation, comparison of PCM and DM systems, noise in PCM and DM systems, Time division multiplexing, Frequency division multiplexing.

### **UNIT II**

**DIGITAL MODULATION TECHNIQUES:** Introduction, ASK, FSK, PSK, DPSK, DEPSK, QPSK, M-ary PSK, ASK, FSK, similarity of BFSK and BPSK.

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## UNIT III

**DATA TRANSMISSION:** Base band signal receiver, probability of error, the optimum filter, matched filter, probability of error using matched filter, coherent reception, non-coherent detection of FSK, calculation of error probability of ASK, BPSK, BFSK, QPSK.

## UNIT IV

**LINEAR BLOCK CODES:** Introduction, Matrix description of Linear Block codes, Error detection and error correction capabilities of Linear block codes, Hamming codes, Binary cyclic codes, Algebraic structure, encoding, syndrome calculation, BCH codes

## UNIT V

**CONVOLUTION CODES:** Introduction, encoding of convolution codes, time domain approach, transform domain approach. Graphical approach: state, tree and trellis diagram decoding using Viterbi algorithm, Turbo Codes.

### TEXT BOOKS:

1. Digital communications - Simon Haykin, John Wiley, 2005.

2. Principles of Communication Systems – H. Taub and D. Schilling, TMH, 2003.

3. Digital Communications- J.Das, S.K.Mullick, P.K.Chatterjee, John willy & sons, 1986.

### REFERENCES:

1. Digital and Analog Communication Systems - Sam Shanmugam, John Wiley, 2005.

2. Digital Communications – John Proakis, TMH, 1983. Communication Systems Analog & Digital – Singh & Sare, TMH, 2004.

3. Modern Analog and Digital Communication – B.P.Lathi, Oxford reprint, 3rd edition, 2004.

### e- Resources:-

- <https://nptel.ac.in/courses/108/105/108105093>

- <https://ocw.mit.edu/courses/6-450-principles-of-digital-communication-i-fall-2006/>

- <https://www.electronics-tutorials.ws/comm/>

Head

Department of ECE

D.N.R. College of Engg. & Tech

BHIMAVARAM-534 207

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

| III Year-I Semester | ANTENNAS AND WAVE PROPAGATION<br>(BT24EC3103) | L | T | P | C |

|---------------------|-----------------------------------------------|---|---|---|---|

|                     |                                               | 3 | 0 | 0 | 3 |

## Course Outcomes:

- Identify basic antenna parameters.

- Quantify the fields radiated by various types of antennas.

- Design and analyze antenna arrays.

- Analyze radiation characteristics and performance of antenna arrays.

- Design and analyze wire antennas, loop antennas, reflector antennas, lens antennas, horn antennas and micro-strip antennas.

- Analyze antenna measurements to assess antenna's performance.

## CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

| CO2 | 3   | 3   | -   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| CO3 | 3   | 3   | 3   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| CO4 | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 2    | 2    |

| CO5 | 3   | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -    | -    | 1    | 3    | 3    |

| CO6 | 3   | 3   | 2   | 3   | 2   | -   | -   | -   | -   | -    | -    | 2    | 2    | 2    |

## UNIT-I:

**ANTENNA FUNDAMENTALS:** Introduction, Radiation Mechanism – Single Wire, 2-Wire, dipoles, Current Distribution on a thin wire antenna. Antenna Parameters - Radiation Patterns, Patterns in Principal Planes, Field Regions, Main Lobe and Side Lobes, Beam width, Radiation Intensity, Directivity, Antenna Efficiency, Gain, Beam Efficiency, Bandwidth, Polarization, Input Impedance, Beam Area and Resolution, Antenna Apertures, Aperture Efficiency, Effective Height, illustrated Problems.

## UNIT-II:

**THIN LINEAR WIRE ANTENNAS:** Retarded Potentials, Radiation from Small Electric Dipole, Quarter wave Monopole and Half wave Dipole – Current Distributions, Evaluation of Field Components, Power Radiated, Radiation Resistance, Radiation Efficiency, Beam width, Directivity, Effective Area and Effective Height. Natural current distributions, fields and patterns of Thin Linear Center-fed Antennas of different lengths, Radiation Resistance at a point which is not current maximum, Antenna Theorems – Applicability and Proofs for equivalence of directional characteristics, Loop Antennas: Small Loops - Field Components, Comparison of far fields of small loop and short dipole, Concept of short magnetic dipole, D and R<sub>r</sub> relations for small loops.

# **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## **UNIT-III:**

**ANTENNA ARRAYS:** 2 element arrays – different cases, Principle of Pattern Multiplication, N element Uniform Linear Arrays – Broadside, End-fire Arrays, EFA with Increased Directivity, Derivation of their characteristics and comparison; Concept of Scanning Arrays. Directivity Relations (no derivations), Related Problems. Binomial Arrays, Effects of Uniform and Non-uniform Amplitude Distributions, Design Relations Arrays with Parasitic Elements, Yagi-Uda Arrays, Folded Dipoles and their characteristics.

## **UNIT-IV**

**BROADBAND ANTENNAS:** Log periodic antenna, Basic principle, Helical Antennas – Significance, Geometry, basic properties; Design considerations for monofilar helical antennas in Axial Mode and Normal Modes (Qualitative Treatment).

## **UHF AND MICROWAVE ANTENNAS:**

**Horn Antennas** – Types, Optimum Horns, Design Characteristics of Pyramidal Horns; **Paraboloidal Reflectors** – Geometry, characteristics, types of feeds, F/D Ratio, Spill Over, Back Lobes, Aperture Blocking, Off-set Feeds, Case grain Feeds.

**Microstrip Antennas**-Introduction, Features, Advantages and Limitations, Rectangular Patch Antennas –Geometry and Parameters, Impact of different parameters on characteristics, illustrated Problems.

## **UNIT-V**

**ANTENNA MEASUREMENTS:** Friis Transmission Equation, Patterns Required, Set Up, Distance Criterion, Directivity and Gain Measurements (Comparison, Absolute and 3-Antenna Methods).

**WAVE PROPAGATION:** TYPES of propagations. Sky Wave Propagation – Formation of Ionospheric Layers and their Characteristics, Mechanism of Reflection and Refraction, Critical Frequency, MUF and Skip Distance; Space Wave Propagation – Mechanism, LOS and Radio Horizon, Field strength equation, illustrated Problems.

## **TEXT BOOKS:**

1. **Antenna Theory: Analysis And Design**- Constantine A. Balanis, 3<sup>rd</sup> Edition, A John Wiley & Sons, Inc., Publication.

2. **Antennas for All Applications** – John D. Kraus and Ronald J. Marhefka, 3<sup>rd</sup> Edition, TMH, 2003.

3. **Electromagnetic Waves and Radiating Systems** – E.C. Jordan and K.G. Balmain, PHI, 2<sup>nd</sup> Edition, 2000.

## **REFERENCES:**

1. **Antennas and Wave Propagation**-G.S.N. Raju, Pearson publications, 2006.

2. **Transmission and Propagation** – E.V.D. Glazier and H.R.L. Lamont, The Services Text Book of Radio, vol. 5, Standard Publishers Distributors, Delhi.

3. **Antennas** – John D. Kraus, McGraw-Hill, 2<sup>nd</sup> Edition, 1988.

## D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

---

### e- Resources:-

- <https://nptel.ac.in/courses/108/102/108102123>

- <https://ocw.mit.edu/courses/6-013-electromagnetics-and-applications-spring-2009/>

- <https://www.electronics-notes.com/articles/antennas-propagation/>

*Veluru Gopal*

Head

Department of ECE

D.N.R. College of Engg. & Tech

BHIMAVARAM-534 202

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

| III Year I Semester | DIGITAL SYSTEM DESIGN THROUGH<br>HDL (PE-I)<br>(BT24EC31P1A) | L | T | P | C |

|---------------------|--------------------------------------------------------------|---|---|---|---|

|                     |                                                              | 3 | 0 | 0 | 3 |

### Course Outcomes:

- Understand the language constructs and programming fundamentals of Verilog HDL.

- Choose the suitable abstraction level for a particular digital design.

- Construct Combinational and sequential circuits in different modelling styles using Verilog HDL.

- Model digital circuits using dataflow and switch-level descriptions in Verilog HDL.

- Design and synthesize combinational and sequential logic circuits.

- Analyze and verify the functionality of digital circuits/systems using test benches.

### CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 2   | -   | -   | -   | -   | -   | -   | -   | -    | 1    | 1    | 1    | 1    |

| CO2 | 3   | 3   | -   | 2   | -   | -   | -   | -   | -   | -    | 1    | 2    | 2    | 2    |

| CO3 | 3   | 3   | 3   | 2   | -   | -   | -   | -   | -   | -    | 1    | 2    | 2    | 2    |

| CO4 | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -   | -    | 1    | 2    | 2    | 2    |

| CO5 | 3   | 3   | 3   | 2   | 2   | -   | -   | -   | -   | -    | 1    | 3    | 3    | 3    |

| CO6 | 3   | 3   | 2   | 3   | 2   | -   | -   | -   | -   | -    | 2    | 2    | 2    | 2    |

### UNIT-I: Introduction to Verilog HDL and Gate Level Modelling:

Verilog as HDL, Levels of Design Description Basics of Concepts of Verilog, Data Types, System Task, Compiler directives, modules and ports. AND Gate Primitive, Module Structure, Other Gate Primitives, Illustrative Examples, Tri-State Gates, Array of Instances of Primitives, Additional Examples, Design of Flipflops with Gate Primitives, Delay.

### UNIT-II: Behavioural Modelling:

Introduction, structured processors, procedural assignments, timing controls, conditional statements, multi-way branching, loops, sequential and parallel blocks, generate blocks, Design of Decoders, Multiplexers, Flip-flops, Registers & Counters in Behavioral model.

### UNIT-III: Modelling at Data flow Level:

Introduction, Continuous Assignment Structures, Delays and Continuous Assignments, Assignment to Vectors, Operators, Design of Decoders, Multiplexers, Flip-flops, Registers & Counters in dataflow model, Switch Level Modelling: Introduction, Basic Transistor Switches, CMOS Switch, Bi-directional Gates, Time Delays with Switch Primitive delays.

# **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## **UNIT-IV: FSM Design:**

Functions, Tasks, User-defined, Primitives: Introduction, Function, Tasks, User-Defined Primitives (UDP), FSM Design (Moore and Mealy Machines), Encoding Style: From Binary to One Hot. Introduction to Synthesis, Synthesis of combinational logic, Synthesis of sequential logic with latches and flip-flops, Synthesis of Explicit and Implicit State Machines.

## **UNIT-V: Components Test and Verification:**

**Test Bench** – Combinational Circuits Testing, Sequential Circuits Testing, Test Bench Techniques, Design Verification, Assertion Verification.

### **Text Books:**

1. Samir Palnitkar, "Verilog HDL A Guide to Digital and Synthesis" ,2<sup>nd</sup> Edition, Pearson Education,2006.

2. Michael, D. Ciletti, "Advanced digital design with the Verilog HDL", Pearson Education India,2005.

### **Reference Books:**

1. Padmanabhan, Tripura Sundari -Design through Verilog HDL, Wiley, 2016.

2. S. Brown, Zvonko – Vranesic, Fundamentals of Digital Logic with Verilog Design, TMH, 3<sup>rd</sup> Edition 2014.

3. J. Bhasker, A Verilog HDL Primer 2<sup>nd</sup> edition, BS Publications, 2001.

### **e- Resources:-**

- <https://nptel.ac.in/courses/108/105/108105132>

- <https://www.asic-world.com/verilog/index.html>

- <https://www.edaplayground.com/>

Arun Gopal

Head

Department of ECE

D.N.R. College of Engg. & Tech

BHIMAVARAM-534 207

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH - CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

| III Year-I Semester | OPTICAL COMMUNICATIONS<br>(BT24EC31P1B) | L | T | P | C |

|---------------------|-----------------------------------------|---|---|---|---|

|                     |                                         | 3 | 0 | 0 | 3 |

### Course Outcomes:

- Illustrate the optical fiber communication along with types of optical fibers.

- Identify various losses and dispersion models.

- Apply splicing techniques on fibers.

- Analyze different types of Optical sources, photo detectors for optical test equipment.

- Evaluate the power coupled in to optical fibers.

- Design optical system with budget analysis.

### CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

| CO2 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

| CO3 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

| CO4 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

| CO5 | 3   | 3   | -   | -   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

| CO6 | -   | 3   | 1   | 2   | -   | -   | -   | -   | -   | -    | -    | -    | -    | 3    |

### UNIT I

Overview of optical fiber communication - Historical development, The general system, advantages of optical fiber communications. Optical fiber waveguides-Introduction, Ray theory transmission, Total Internal Reflection, Acceptance angle, Numerical Aperture, Skew rays, cylindrical fibers- Modes, V-number, Mode coupling, Step Index fibers, Graded Index fibers, Single mode fibers-Cutoff wavelength, Mode Field Diameter, Effective Refractive Index, Related problems.

### UNIT II

Fiber materials: - Glass, Halide, Active glass, Chalgenide glass, Plastic optical fibers. Signal distortion in optical fibers-Attenuation, Absorption, Scattering and Bending losses, Core and Cladding losses, Information capacity determination, Group delay, Types of Dispersion: - Material dispersion, Wave-guide dispersion, Polarization-Mode dispersion, Intermodal dispersion, Pulse broadening in Graded index fiber, Related problems.

### UNIT III

Optical fiber Connectors-Connector types, Single mode fiber connectors, Connector return loss, Fiber Splicing-Splicing techniques, Splicing single mode fibers, Fiber alignment and joint loss- Multimode fiber joints, single mode fiber joints.

# **D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS**

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

## **UNIT IV**

Optical sources-LEDs, Structures, Materials, Quantum efficiency, Power, Modulation, Power bandwidth product. Injection Laser Diodes- Modes, Threshold conditions, External quantum efficiency, Laser diode rate equations, Resonant frequencies, Reliability of LED&ILD, Optical detectors- Physical principles of PIN and APD, Detector response time, Comparison of Photo detectors, Related problems.

## **UNIT V**

Source to fiber power launching - Output patterns, Power coupling, Power launching, Equilibrium Numerical Aperture, Laser diode to fiber coupling, Optical receiver operation- Fundamental receiver operation, Digital signal transmission, error sources, Receiver configuration, Digital receiver performance, Probability of Error, Quantum limit, Analog receivers. Optical system design - Point-to- point links- Component choice and considerations, Link power budget, Rise time budget with examples, Line coding in Optical links, WDM, Necessity, Principles, Measurement of Attenuation and Dispersion, Eye pattern.

## **TEXTBOOKS:**

1. Optical Fiber Communications—Gerd Keiser, Mc Graw-Hill International edition, 3<sup>rd</sup> Edition, 2000.

2. Fiber Optic Communications— Joseph C.Palais, 4<sup>th</sup> Edition, Pearson Education, 2004.

## **REFERENCES:**

1. Fiber Optic Communications—D.K.Mynbaev, S.C.Gupta and Lowell L.Scheiner, Pearson Education, 2005.

2. Text Book on Optical Fiber Communication and its Applications—S.C.Gupta, PHI, 2005.

3. Fiber Optic Communication Systems—Govind P. Agarwal ,John Wiley, 3<sup>rd</sup> Edition, 2004.

## **e- Resources:-**

- <https://nptel.ac.in/courses/108/106/108106108>

- <https://ocw.mit.edu/courses/6-979-optical-communications-spring-2006/>

- [https://www.rp-photonics.com/optical\\_fiber\\_communications.html](https://www.rp-photonics.com/optical_fiber_communications.html)

**Head**

**Department of ECE**

**D.N.R. College of Engg. & Tech**

**BHIMAVARAM-534 207**

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A++ Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

| III Year I Semester | ELECTRONIC MEASUREMENTS AND<br>INSTRUMENTATION<br>(BT24EC31P1C) | L | T | P | C |

|---------------------|-----------------------------------------------------------------|---|---|---|---|

|                     |                                                                 | 3 | 0 | 0 | 3 |

### Course Outcomes:

- Understand the various Analog and Digital measuring Instruments.

- Aware of the principles and operations of various oscilloscopes.

- Learn measurements using DC bridges.

- Learn measurements using AC bridges.

- Familiarize different Signal Generators and function generators.

- Learn various transducers and intelligent sensors.

### CO-PO/PSO MATRIX: (Level of Mapping- 3: High; 2: Moderate; 1-Low; -: Not mapped)

| CO  | PO1 | PO2 | PO3 | PO4 | PO5 | PO6 | PO7 | PO8 | PO9 | PO10 | PO11 | PO12 | PSO1 | PSO2 |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|

| CO1 | 3   | 2   | 2   | 1   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

| CO2 | 3   | 2   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

| CO3 | 3   | 1   | 1   | 1   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | -    |

| CO4 | 3   | 3   | 1   | 1   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | -    |

| CO5 | 3   | 1   | 1   | 1   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

| CO6 | 3   | 2   | 2   | 2   | -   | -   | -   | -   | -   | -    | -    | 1    | 1    | 1    |

### UNIT I

**Measuring Instruments:** Introduction, Errors in Measurement, Accuracy, Precision, Resolution and Significant figures, Basic PMMC Meter- construction and working, DC and AC Voltmeters- Multirange, Range extension, DC Ammeter, Multimeter for Voltage, Current and resistance measurements.

**Digital Instruments:** Digital Voltmeters – Introduction, DVM's based on V-T, V-F and Successive approximation principles, Resolution and sensitivity, General specifications, Digital Multimeters, Digital frequency meters, Digital measurement of time.

### UNIT II

**Oscilloscopes:** Introduction, Block diagram of CRO, Basic principle of CRT, CRT Construction and features, vertical amplifiers, horizontal deflection system- sweep, trigger pulse, delay line, sync selector circuits. Dual beam and dual trace CROs, Sampling and Digital storage oscilloscopes.

### UNIT III

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

**Bridges:** DC Bridges for Measurement of resistance - Wheat stone bridge, Kelvin's Bridge, AC Bridges for Measurement of inductance- Maxwell's bridge, Hay's Bridge, Anderson bridge, Measurement of capacitance - Schering Bridge, Wien Bridge, Errors and precautions in using bridges.

## UNIT IV

**Signal Generators:** Introduction, Fixed and variable AF oscillator, Standard signal generator, Laboratory type signal generator, AF sine and Square wave generator, Function generator, Square and Pulse generator, Sweep frequency generator.

## UNIT V

**Transducers:** Introduction, Types of Transducers, Electrical transducers, Selecting a transducer, Resistive transducer, Strain gauges, Piezoelectric transducer, Photoelectric transducer, Photovoltaic transducer, Temperature transducers-RTD, LVDT.

**Intelligent Sensors:** definition of intelligent instrumentation, types of instruments, Classification, Smart sensors, Cogent Sensors, Soft or Virtual sensors, Self-Adaptive Sensors, Self-Validating Sensors, Temperature Compensating Intelligent Sensors, Pressure Sensor, Indirect Sensing. (Text Book 3).

## TEXT BOOKS

1. H. S. Kalsi, "Electronic Instrumentation", Third edition, Tata McGraw Hill, 2010.

2. A. D. Helfrick and W.D. Cooper, "Modern Electronic Instrumentation and Measurement Techniques", PHI, 6th Edition, 2010.

3. Manabendra Bhuyan, —Intelligent Instrumentation: Principles and Applications CRC Press, 2011.

## REFERENCE BOOKS

1. A.K. Sawhney, Dhanpat Rai & Co., "A course in Electrical and Electronic Measurements and Instrumentation", 9<sup>th</sup> Edition, 2010.

2. David A. Bell, "Electronic Instrumentation & Measurements", PHI, 2nd Edition, 2006.

## e- Resources:-

- <https://nptel.ac.in/courses/108/106/108106146>

- <https://ocw.mit.edu/courses/res-6-010-electronic-measurements-spring-2004/>

- <https://www.electronics-tutorials.ws/measurement/>

# D.N.R. COLLEGE OF ENGINEERING & TECHNOLOGY

## AUTONOMOUS

Approved by AICTE, New Delhi & Permanently Affiliated to JNTUK, Kakinada

Accredited with A<sup>++</sup> Grade by NAAC & Accredited by NBA (B. TECH – CSE, ECE & EEE)

Ph: 08816-221238 Email: [dnrcet@gmail.com](mailto:dnrcet@gmail.com) website: <https://dnrcet.org>

|                            |                                                                     |          |          |          |          |

|----------------------------|---------------------------------------------------------------------|----------|----------|----------|----------|

| <b>III Year I Semester</b> | <b>COMPUTER ORGANIZATION AND<br/>ARCHITECTURE<br/>(BT24EC31P1D)</b> | <b>L</b> | <b>T</b> | <b>P</b> | <b>C</b> |

|                            |                                                                     | <b>3</b> | <b>0</b> | <b>0</b> | <b>3</b> |

### Course Outcomes: